Here’s how the RTL Schematic will look if we peek into the elaborate design of the behavioral model of the D-flip flop without clear input.

$monitor("simtime = %g, CLK = %b, D = %b,reset = %b, Q = %b, QBAR = %b", $time, CLK, D, reset, Q, QBAR) We have instantiated the dff_behaviorĭff_behavior dut(.q(Q). Let’s see how we can write a test bench for D-flip flop by following step by step instruction //test bench for d flip flop The input and desired output patterns are called test vectors. The test bench contains statements to apply inputs to the DUT and, ideally, to check that the correct outputs are produced.

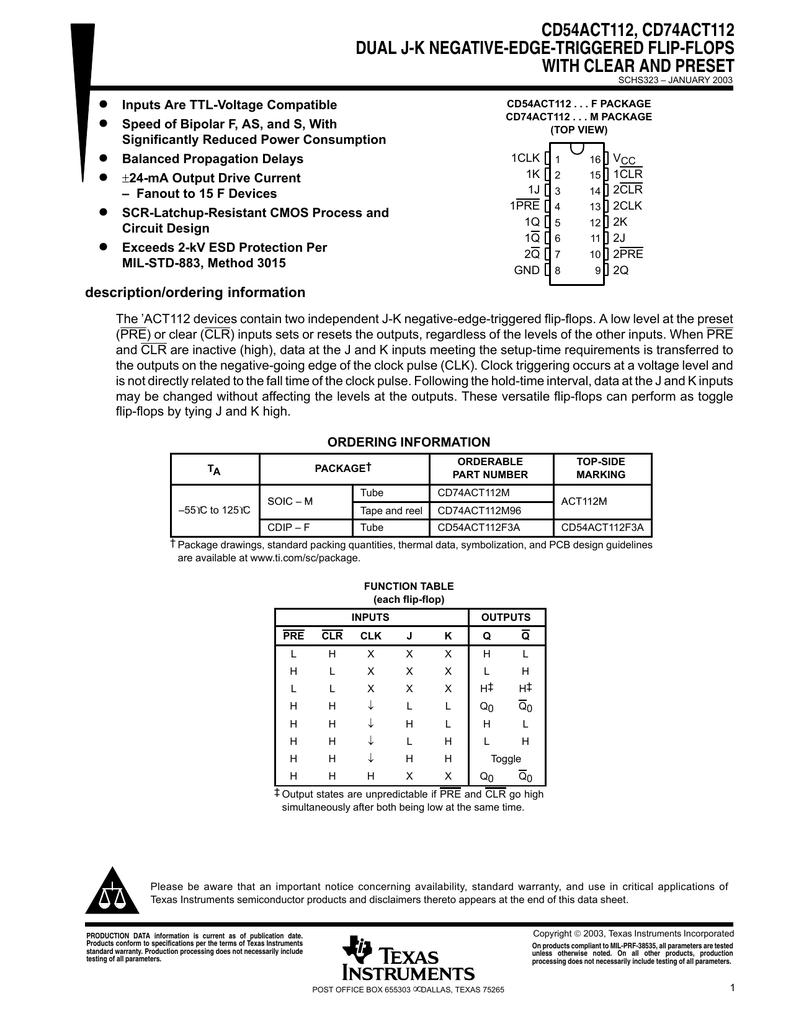

NEG EDGE TRIGGERED FLIP FLOP CODE

Hence, the final structure code will be: module nand_gate(c,a,b) Ī testbenchis an HDL module that is used to test another module, called the device under test ( DUT). The port-list will contain the output signals, followed by the input ones.ĭo the same for the rest of the instances First, start with the name of the lower hierarchy module (defined and declared above) and write the name of the instance of your choice. In order to do that, we use module instantiation. Now, we have to integrate these lower modules to form our D-flip flop. This ensures mixing up of signals does not happen during a simulation. Note: We keep variables for assigning inputs and outputs in one module different from others. In the case of D-flip flop, we have a NOT and four NAND gates that build the circuit.

But, instead of using in-built gates, we take each gate and create separate modules that will be integrated to form the whole circuitry. We will consider the gates required to build the design. Like in Gate level modeling, we analyze the logic design for structural modeling. Hence we write our code as: module dff_behavioral(d,clk,clear,q,qbar) Negative Edge Triggered D flip flop Verilog Code module posedgedf (q, din, clkin, rstin) // this module define d flip flop with q as output and data, clock and reset as input // input din, clkin, rstin / input variable of the d flip flop is defined output reg q / output variable of the d flip flop is defined always (negedge clkin) / this block is implemented continuously with. This can be achieved by adding a clear signal to the sensitivity list. Here, as soon as clear input is activated, the output reset. Here’s the code: module dff_behavioral(d,clk,clear,q,qbar) īehavioral Modeling of D flip flop with Asynchronous Clearįor asynchronous clear, the clear signal is independent of the clock. Behavioral Modeling of D flip flop with Synchronous Clearįor synchronous clear, the output will reset at the triggered edge(positive edge in this case) of the clock after the clear input is activated. This clear input becomes handy when we tie up multiple flip flops to build counters, shift registers, etc. Hence, we will include a clear pin that forces the flip flop to a state where Q = 0 and Q’ = 1 despite whatever input we provide at the D input.

All hardware systems should have a pin to clear everything and have a fresh start.

0 kommentar(er)

0 kommentar(er)